Como en todos los ámbitos de la modernidad y la automatización, los sistemas sufren el avasallamiento de las tecnologías que no cesan de crecer, incorporando para ello una producción masificante de dispositivos de almacenamiento de increíbles densidades, o vehículos de comunicación de velocidad casi ilimitada.

Las tendencias actuales vienen produciendo incansables cambios progresivos en todas las metodologías de sistemas. En el caso del diseño, el incremento creciente de la complejidad obliga a limitar el tiempo de los ciclos de vida y por ende el desarrollo de los diseños, imponiendo al mismo tiempo la necesidad de contemplar cierto grado de flexibilidad poco habitual en los estándares de desarrollo de modo que permita, además, aceptar posibles modificaciones o actualizaciones en plazos más cortos que los normalmente estimados.

Soluciones basadas en prestaciones crecientes en términos de capacidad y velocidad y su intrínseca flexibilidad en las opciones de implementación vienen ganando terreno en el área de la llamada “computación reconfigurable”, un nuevo paradigma de computación que convierte a su vez a los sistemas en reconfigurables tales que –una vez instalados– pueden ser dinámicamente reconstruidos total o parcialmente debido a que utilizan hardware cuya funcionalidad puede modificarse en tiempo de ejecución, brindando enorme flexibilidad sin comprometer el desempeño del resto del sistema.

Los reconfigurables, sistemas que combinan una componente reconfigurable con un procesador tradicional, pueden generar una configuración óptima para cada una de las tareas que conforman una aplicación pero sin interrumpir su operación, cumpliendo con sus restricciones. y lo que es más espectacular, ubicando de esa manera los elementos del hardware de un sistema dentro de un único chip.

Las especiales cualidades de estas arquitecturas representan una alternativa inmejorable respecto de otros procesadores de propósito general como los procesadores digitales de señal y los Circuitos Integrados de Aplicación Específica, a los cuales dejó atrás por su novedosa y explosiva capacidad para aplicaciones de alto grado de paralelismo de datos y requisitos de procesamiento de alto desempeño como procesamiento de imágenes, video, señales, multimedia y encriptación de datos.

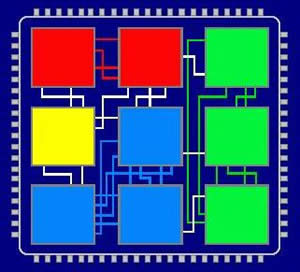

El propósito más importante de los sistemas reconfigurables es dejar la libertad de adaptar el hardware a las aplicaciones que se requieran. Las unidades básicas sobre la que se construye esta arquitectura son los “bloques lógicos” y una matriz configurable de conexiones en red sobre la que se efectúa la transferencia de información y que interconecta a esos bloques según la necesidad del Programador.

Esto elimina la obligatoriedad de conexiones específicas obviando el proceso de manufactura determinística de los circuitos, agregándoseles las funciones lógicas y aritméticas requeridas, así como bloques de memoria. Se completa así la idea de un sistema completo “programable y ejecutable en un chip”.

La clave de este espectacular desarrollo es su componente principal, el “FPGA” (field programmable gate array, o Matriz de Compuertas Programables en la Instalación). La mayoría de los FPGA modernos soporta la reconfiguración parcial del sistema, permitiendo que una parte del diseño sea reprogramada mientras las demás partes continúan funcionando.

Esta reconfiguración se realiza en los bloques lógicos (CLB=”Configurable Logic Block”) de una matriz que puede contener desde decenas de miles hasta millones de bloques en cuyas celdas RAM se almacenan los valores lógicos adecuados. Si se hace en tiempo de ejecución se la llamará “dinámica” y las configuraciones programadas posibles de usarse son ubicadas en una memoria interna de la máquina de modo que cuando se necesite una nueva configuración se carga desde la memoria interna de modo más rápido que desde una externa.

Un CLB típico consiste en una tabla de funciones lógicas de cuatro entradas, un flip-flop y una salida que puede conectarse a cualquier segmento de cable en el canal de comunicación adyacente a ella. Mediante la selección de conexiones a través de interruptores programables se pueden crear líneas de comunicación que atraviesen varios bloques, generando operaciones más complejas. La tarea del programador es definir la función lógica que realizará cada uno de los CLB y crear las interfaces con los pines que servirán de entrada o de salida de los CLB. La FPGA se apoya en lenguajes específicos de descripción de hardware (HDL, hardware description languajes), o en esquemas de programación tradicionales del mercado.

Las cifras de CLBs antes referidas indican que FPGA da opciones para una enorme, casi infinita cantidad de circuitos que permiten multitud de combinaciones de configuración, todo lo cual se refleja dramáticamente en los diseños de sistemas. Cualquier circuito de aplicación específica puede ser implementado en un FPGA mientras se disponga de los recursos necesarios. Los más comunes incluyen al procesamiento digital de señales, emisiones de radio definidas por software, sistemas aeroespaciales y de defensa, sistemas de imágenes para medicina, de visión para computadoras, reconocimiento de voz, emulación de hardware, múltiples de bioinformática, y muy especialmente en aquellas aplicaciones que requieren alto grado de paralelismo.